大家好,我们是华芯极客队,报名编号是CICC3877,本次给大家介绍的是利用Verdi调试协处理器的实现步骤。

有时为了观察协处理器运行情况,需要查看协处理器接口的信号波形,此时可以用Verdi来查看主处理器发给协处理器的自定义指令以进一步追踪协处理器内部信号的执行情况。

1、环境准备

调试过程在Ubuntu系统下进行,需准备好vcs和Verdi软件。另外需要按照《RISC-V架构与嵌入式开发快速入门》一书中的方法,将写好的软件代码进行编译并生成缩写名为verilog的测试文件,通过vcs仿真并生成波形文件,为接下来调试波形做准备。

2、实施步骤

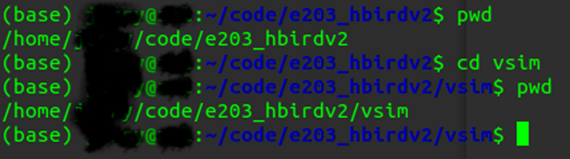

第一步,输入“cd vsim”,进入工程目录下的vsim文件夹内。

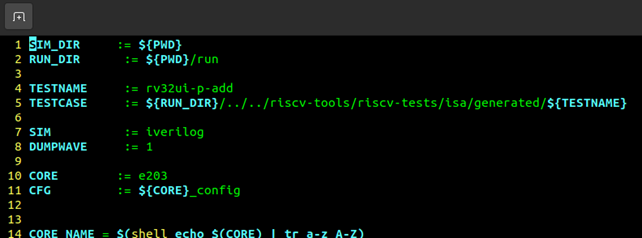

第二步,修改Makefile文件,指明编译生成的可读入测试文件路径。

如图所示,第四行“TESTNAME”为测试文件的名称,此处不需要加缩写名verilog。第五行为测试文件所在路径。

修改完毕后保存并退出。

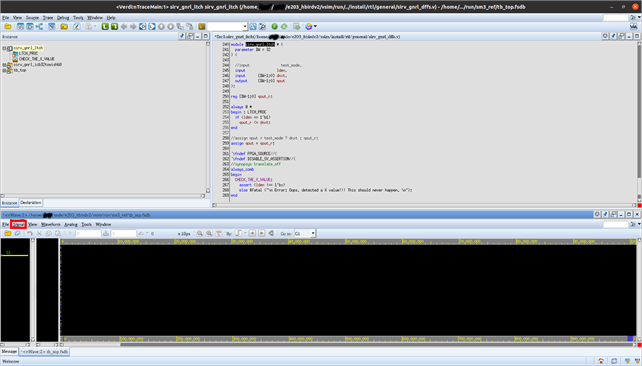

第三步,完成rtl源码编译后输入“make wave”,此时会启动Verdi并读入测试脚本,完成后将会出现如下画面。

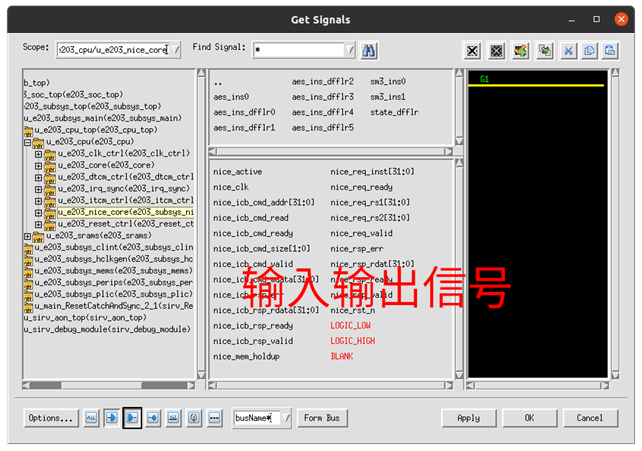

如图所示,选择红色方框标注的Signal,在下拉菜单中选择Get Signals,在下面弹出的对话框中选择要跟踪的信号。

第四步,

选中nice_req_inst[31:0]、nice_req_rs1[31:0]、nice_req_rs2[31:0]观察主处理器发给协处理器的指令和两个源操作数。

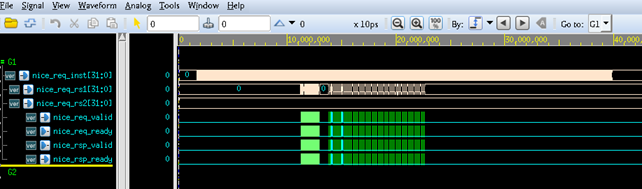

第五步,上一步选中的信号将会在如下图所示的窗口中显示出来。

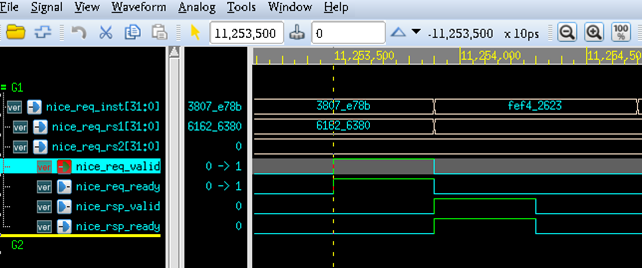

为了看清楚具体的信号,选择工具栏上的放大镜按钮放大波形。放大后的波形不便于寻找调用时刻,可以使用工具栏上的search forward工具按钮搜索nice_req_valid信号以追踪到主处理器发起的调用请求信号。

结果如下图所示。

小结

本文梳理了调试过程中的技巧,通过调试发现协处理器设计不周到的地方,因为能力有限,若是理解不正确的地方请大家指正,共同学习,祝各参赛队取得理想的成绩。