队伍编号:CICC1905 团队名称:青稞战队

本设计的DES控制模块是使用有限状态机(FSM)实现的。FSM的现态是边沿触发的,根据rst_n复位信号和start启动信号进行现态的赋值;次态逻辑设计是S0-S17的次态跳转;输出逻辑设计是控制不同状态的逻辑输出进而控制其它模块工作,所输出的信号均为运算模块和子密钥产生模块工作所需的控制信号。

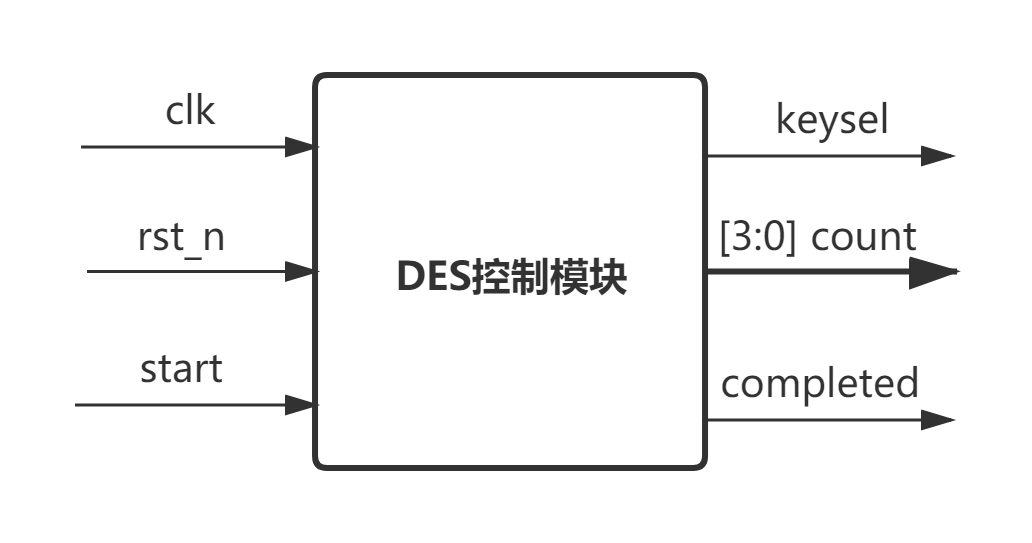

对于DES控制模块,其外框图见图3-3所示,外部信号定义见表3-6所示。

图3-3 DES控制模块外框图

Fig.3-3 Frame diagram of DES control module

表3-6 DES控制模块外部信号定义

Tab.3-6 DES control module external signal definition

信号名称 | 信号方向 | 宽度 | 信号描述 |

clk | input | 1 | 时钟信号,上升沿有效 |

rst_n | input | 1 | 复位信号,低电平有效 |

start | input | 1 | 加解密使能信号,高电平有效 |

keysel | output | 1 | 二选一选通器控制信号,1为初始置换结果,0为中间结果 |

count | output | 4 | 轮密钥选择控制信号 |

completed | output | 1 | 加密/解密完成信号,1为完成加密或解密运算 |

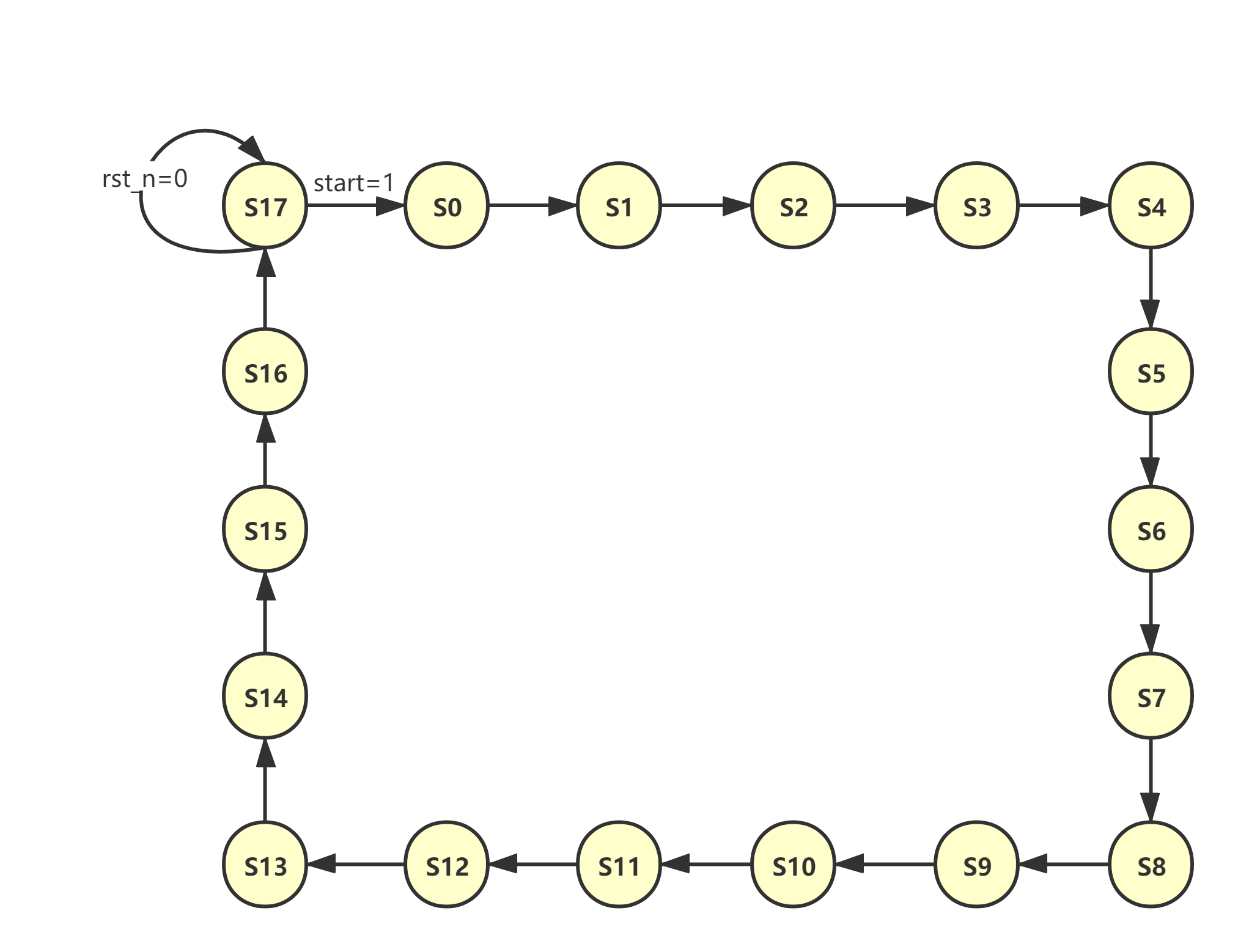

整个FSM使用S0-S17共18个状态,其中,S17是初始状态,无论电路处于何种状态,只要rst_n复位信号有效都将跳转至初始状态;S0-S15为控制协处理器进行加密运算;S16为延迟一个时钟的空转状态,用于配合运算数据从协处理器写回至E203处理器内核中。S0-S17的状态跳转见图3-4所示。此外,为减小状态转换过程中出现的噪音,本设计的状态编码采用格雷码,状态名称与状态编码如下表3-7所示。控制模块的状态转移和控制信号逻辑输出见表3-8所示。

图3-4 控制模块FSM状态跳转

Fig.3-4 FSM status jump of control module

表3-7 DES控制模块状态编码

Tab.3-7 DES control module status coding

状态名称 | 状态编码 | 状态名称 | 状态编码 | 状态名称 | 状态编码 |

S0 | 00000 | S6 | 00101 | S12 | 01010 |

S1 | 00001 | S7 | 00100 | S13 | 01011 |

S2 | 00011 | S8 | 01100 | S14 | 01001 |

S3 | 00010 | S9 | 01101 | S15 | 01000 |

S4 | 00110 | S10 | 01111 | S16 | 11000 |

S5 | 00111 | S11 | 01110 |

表3-8 DES控制模块FSM的状态转移和控制信号逻辑输出

Tab.3-8 State transition and control signal logic output of DES control module F

现态 | 输入 | 次态 | 输出 |

S17(IDLE) | rst_n=0 | S17 | keysel=1,count=0,completed=1 |

S17 | start=1 | S0 | keysel=1,count=0,completed=1 |

S0 | start=1 | S1 | keysel=1,count=0,completed=0 |

S1 | start=1 | S2 | keysel=0,count=1,completed=0 |

S2 | start=1 | S3 | keysel=0,count=2,completed=0 |

S3 | start=1 | S4 | keysel=0,count=3,completed=0 |

S4 | start=1 | S5 | keysel=0,count=4,completed=0 |

S5 | start=1 | S6 | keysel=0,count=5,completed=0 |

S6 | start=1 | S7 | keysel=0,count=6,completed=0 |

S7 | start=1 | S8 | keysel=0,count=7,completed=0 |

S8 | start=1 | S9 | keysel=0,count=8,completed=0 |

S9 | start=1 | S10 | keysel=0,count=9,completed=0 |

S10 | start=1 | S11 | keysel=0,count=10,completed=0 |

S11 | start=1 | S12 | keysel=0,count=11,completed=0 |

S12 | start=1 | S13 | keysel=0,count=12,completed=0 |

S13 | start=1 | S14 | keysel=0,count=13,completed=0 |

S14 | start=1 | S15 | keysel=0,count=14,completed=0 |

S15 | start=1 | S16 | keysel=0,count=15,completed=0 |

S16 | start=1 | S17 | keysel=0,count=0,completed=1 |