为应对RISC-V在智能卡等高安全应用场景中面临的安全要求不统一、标准缺失等行业共性问题,《白皮书》首次系统性构建覆盖智能卡RISC-V处理器全链路的安全技术体系,填补了国内相关领域技术标准的空白。

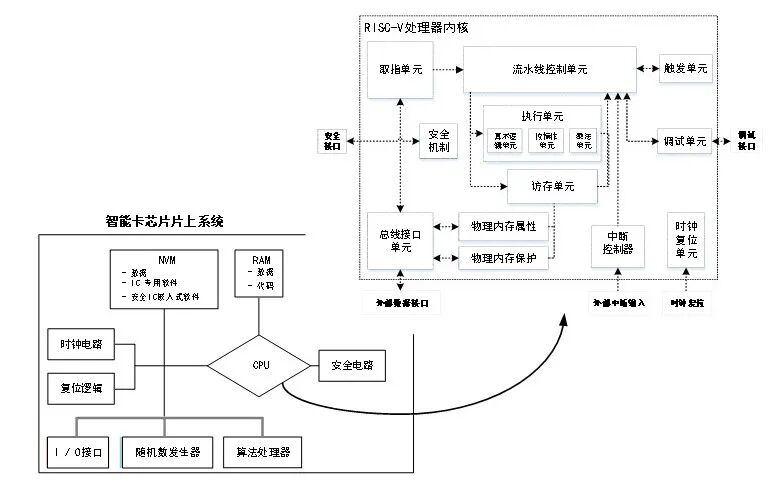

《白皮书》针对基于RISC-V架构智能卡芯片中RISC-V处理器提出安全要求。智能卡RISC-V处理器是智能卡的核心功能模块,其是信息处理和程序运行的最终执行单元,也可以支撑密码算法协处理器等专用模块,共同实现智能卡的安全功能。智能卡RISC-V处理器内核的一般功能结构如下图所示:

《白皮书》系统梳理出18项安全增强机制的技术框架,涵盖内存泄露管控、权限分级控制、统一分支定时、随机执行周期、随机指令等,构建了覆盖信息泄露防护、故障注入抵御、逻辑攻击防范等全方位安全能力,为智能卡RISC-V处理器的设计、验证和应用提供了全链路安全防护体系。

如需了解详情,可查看白皮书全文:

下载链接:

https://yun.139.com/shareweb/#/w/i/2qidEhQ3YsP7z

提取码:pqks

作为本土RISC-V领域的代表性企业,芯来科技长期深耕通用以及适用于各类垂直领域的处理器IP研发。本次芯来科技深度参与《白皮书》的技术架构、安全要求等关键环节,为白皮书的技术性、完整性、实用性和前瞻性提供了专业支持与贡献,希望能为产业在规划设计RISC-V处理器相关技术、产品和解决方案时提供参考和指引。

在安全应用领域,芯来科技NS系列面向高安全场景,涵盖了丰富的安全特性以及抗侧信道攻击的防护能力,能更好地保护万物互联时代下智慧连接设备的信息安全。同时为全面提升信息安全合规体系建设效能,芯来科技于25年3月正式纳入Common Criteria(CC)认证预审核站点体系。该站点基于国际通用评估准则(ISO/IEC 15408)建立前置性评估机制,此站点审核为芯来客户的CC认证提供全流程加速支持。

未来,芯来科技将继续携手中国移动及产业链伙伴,共同推动《白皮书》技术成果实现产业化落地,不断完善智能卡RISC-V架构安全技术标准,并与产业链上下企业为行业高质量发展共同努力,向产业持续输出更加优质的产品。